3D Integrated Circuit (3D IC)

3D Integrated Circuit (3D IC)

เทคโนโลยีอุปกรณ์คอมพิวเตอร์ในอดีตจนถึงปัจจุบันมีแนวโน้มเป็นไปตามการคาดการณ์หรือทฤษฎีของ Moore ที่กล่าวว่า จำนวนทรานซิสเตอร์บนชิปซิลิกอนจะเพิ่มขึ้น 2 เท่าในทุกปี เพื่อเพิ่มความสามารถในการประมวลผลของชิป ทำให้เทคโนโลยีการสร้างชิป หรือ วงจรรวม หรือ Integrated Circuit (IC) ใช้การขยายขนาดตัว IC และย่อขนาดชิ้นส่วนภายใน IC ให้มีขนาดเล็กลง เพื่อให้ IC แต่ละตัว สามารถบรรจุทรานซิสเตอร์จำนวนมาก ๆ ได้ โดยปัจจุบันขนาดเทคโนโลยีการสร้าง IC จะอยู่ที่ประมาณ 5 nm และมีแผนการลดขนาดลงให้ได้ 3 และ 2 nm ตามลำดับ แต่การสร้าง IC ที่เน้นการลดขนาดชิ้นส่วนภายใน IC นั้นก็มีข้อจำกัดด้านการลดขนาดเทคโนโลยี โดยนักวิทยาศาสตร์เล็งเห็นถึงปัญหาการลดขนาดทรานซิสเตอร์ที่อาจจะทำไม่ได้ในระยะเวลาอันสั้น อีกทั้งการเพิ่มขนาด IC ก็มีผลเสียทำให้การประมวลผลช้าลงเนื่องจากระยะการรับส่งข้อมูลเพิ่มขึ้นนั่นเอง

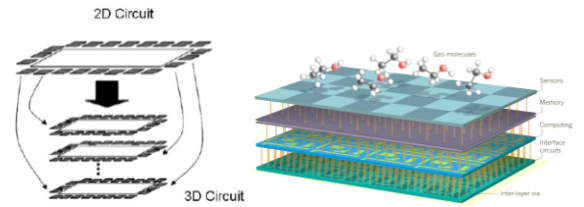

เพื่อเป็นการแก้ปัญหาพื้นที่ในการจัดเก็บชิ้นส่วนวงจรไฟฟ้าภายในของ IC จึงมีการคิดค้นเทคโนโลยีวงจรรวมสามมิติ หรือ 3D IC ขึ้นมา ลักษณะการจัดวางชิ้นส่วนภายใน IC จะมีลักษณะคล้ายอาคารหลายชั้น โดยแต่ละชั้นจะเป็นวงจรไฟฟ้าสำหรับเชื่อมต่อการทำงานต่าง ๆ กันไปขึ้นอยู่กับการออกแบบวงจรของผู้ผลิต และมีเส้นทางเชื่อมต่อรับส่งข้อมูลระหว่างชั้นลักษณะคล้ายเสาของอาคาร ซึ่งช่วยลดระยะทางในการรับส่งข้อมูลภายใน IC เมื่อเปรียบเทียบกับ 2D IC แบบเดิม ทำให้การรับส่งข้อมูลเป็นไปอย่างรวดเร็ว ส่งผลสืบเนื่องให้การประมวลผลต่าง ๆ เป็นไปอย่างรวดเร็วขึ้นด้วย การออกแบบของ 3D IC ยังช่วยลดปริมาณไฟฟ้าที่ต้องใช้ใน IC เนื่องจากระยะการส่งข้อมูลที่สั้น ทำให้ไม่ต้องใช้พลังงานไฟฟ้าที่สูงในการรับส่งข้อมูล เมื่อเทียบกับวงจรแบบเก่า

อย่างไรก็ตาม การอออกแบบ 3D IC เทียบกับ 2D IC มักจะพบปัญหาความร้อนที่เกิดขึ้นจากวงจรไฟฟ้าขนาดใหญ่ที่มีความซับซ้อนมากขึ้น รวมถึงปัญหาในการออกแบบระบบถ่ายเทความร้อนจากวงจรแต่ละชั้น อีกทั้งยังเป็นความท้าทายในการออกแบบเส้นทางส่งสัญญาณระหว่างชั้นให้มีระยะทางที่สั้นที่สุดและไม่ทับซ้อนกันกับเส้นทางการส่งข้อมูลอื่น ๆ อีกด้วย

chgate.net และ https://media.springernature.com

เพื่อเป็นการแก้ปัญหาพื้นที่ในการจัดเก็บชิ้นส่วนวงจรไฟฟ้าภายในของ IC จึงมีการคิดค้นเทคโนโลยีวงจรรวมสามมิติ หรือ 3D IC ขึ้นมา ลักษณะการจัดวางชิ้นส่วนภายใน IC จะมีลักษณะคล้ายอาคารหลายชั้น โดยแต่ละชั้นจะเป็นวงจรไฟฟ้าสำหรับเชื่อมต่อการทำงานต่าง ๆ กันไปขึ้นอยู่กับการออกแบบวงจรของผู้ผลิต และมีเส้นทางเชื่อมต่อรับส่งข้อมูลระหว่างชั้นลักษณะคล้ายเสาของอาคาร ซึ่งช่วยลดระยะทางในการรับส่งข้อมูลภายใน IC เมื่อเปรียบเทียบกับ 2D IC แบบเดิม ทำให้การรับส่งข้อมูลเป็นไปอย่างรวดเร็ว ส่งผลสืบเนื่องให้การประมวลผลต่าง ๆ เป็นไปอย่างรวดเร็วขึ้นด้วย การออกแบบของ 3D IC ยังช่วยลดปริมาณไฟฟ้าที่ต้องใช้ใน IC เนื่องจากระยะการส่งข้อมูลที่สั้น ทำให้ไม่ต้องใช้พลังงานไฟฟ้าที่สูงในการรับส่งข้อมูล เมื่อเทียบกับวงจรแบบเก่า

อย่างไรก็ตาม การอออกแบบ 3D IC เทียบกับ 2D IC มักจะพบปัญหาความร้อนที่เกิดขึ้นจากวงจรไฟฟ้าขนาดใหญ่ที่มีความซับซ้อนมากขึ้น รวมถึงปัญหาในการออกแบบระบบถ่ายเทความร้อนจากวงจรแต่ละชั้น อีกทั้งยังเป็นความท้าทายในการออกแบบเส้นทางส่งสัญญาณระหว่างชั้นให้มีระยะทางที่สั้นที่สุดและไม่ทับซ้อนกันกับเส้นทางการส่งข้อมูลอื่น ๆ อีกด้วย

เว็บไซต์มหาวิทยาลัย : www.npru.ac.th

เว็บไซต์สาขาวิชา : http://pgm.npru.ac.th/ct/

ดูประวัติผู้เขียน : http://pws.npru.ac.th/pitiphol/

ความคิดเห็น

แสดงความคิดเห็น